- 您现在的位置:买卖IC网 > Sheet目录1220 > IP-SDRAM/DDR2 (Altera)IP DDR2 SDRAM CONTROLLER

�� �

�

�

�3–22�

�Chapter� 3:� Functional� Description�

�Interfaces� &� Signals�

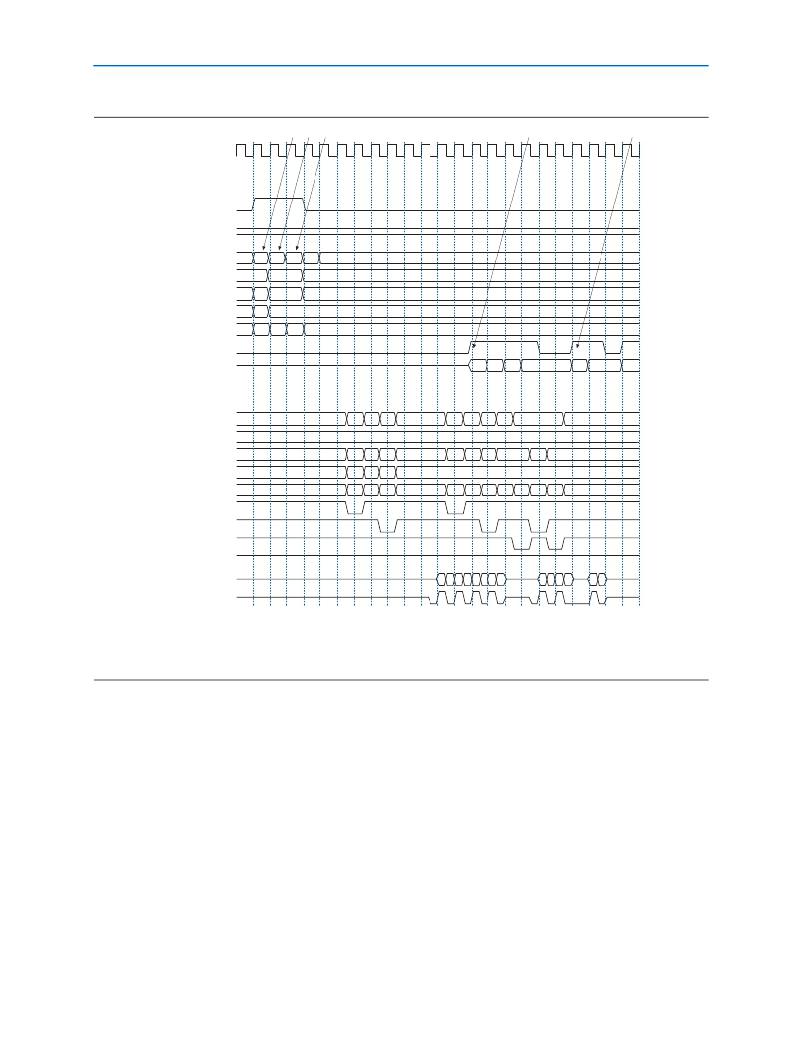

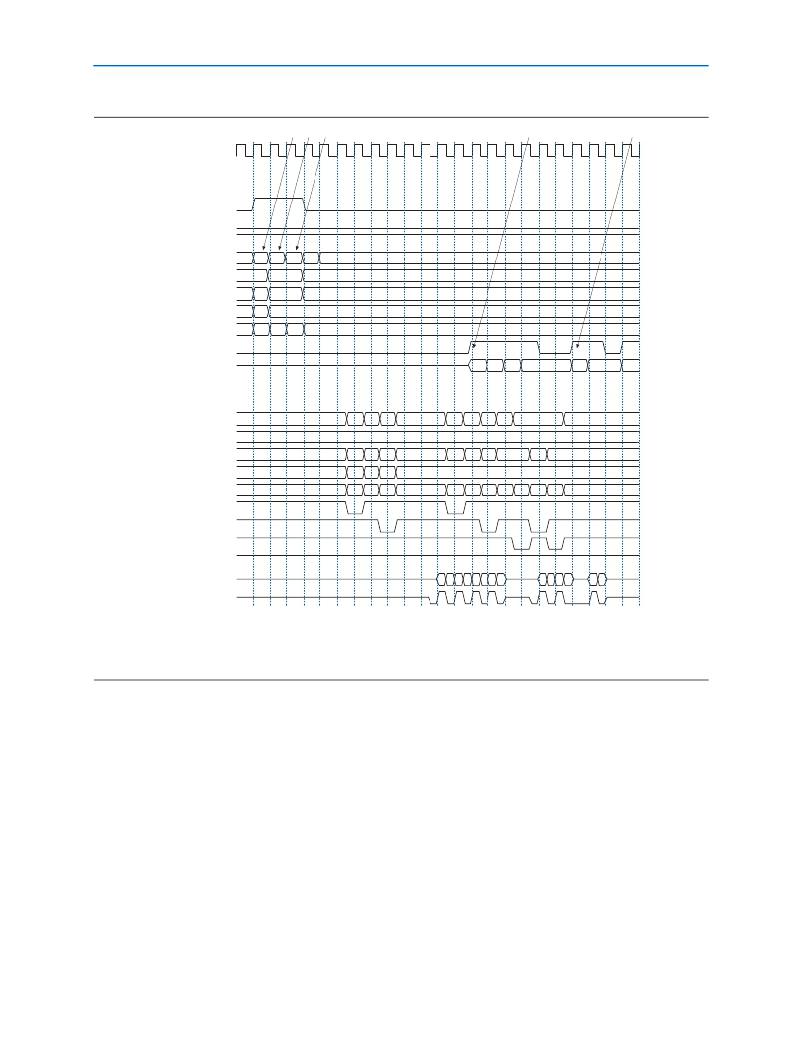

�Figure� 3–14.� Reads�

�[1]� [2]�

�[3]�

�[4]�

�[5]�

�clk�

�Local� Interface�

�local_read_req�

�local_write_req�

�local_ready�

�local_size�

�0�

�4�

�2�

�1�

�0�

�local_cs_addr� (1)�

�local_row_addr� (1)�

�0�

�170�

�1�

�040�

�0�

�000�

�local_bank_addr� (1)�

�local_col_addr� (1)�

�0�

�1�

�050� 055� 057�

�0�

�000�

�local_rdata_valid�

�local_rdata�

�534� 8� 8� 6F4�

�D310�

�77F4�

�0479�

�54B0�

�CB4� 8�

�DDR� SDRAM�

�Interface�

�ddr_cs_n�

�F�

�E�

�F�

�E�

�F�

�D�

�F�

�D�

�F�

�D�

�F�

�ddr_cke�

�F�

�ddr_a�

�ddr_ba�

�000�

�0�

�170� 000� 0A0�

�1�

�0�

�1�

�000�

�040� 000� 0AA�

�000�

�0�

�0AE�

�000�

�DDR� Command� (2)�

�NOP�

�ACT�

�NOP�

�RD�

�NOP�

�ACT�

�NOP�

�RD�

�NOP�

�BT� RD� BT�

�NOP�

�ddr_ras_n�

�ddr_cas_n�

�ddr_we_n�

�ddr_dm�

�ddr_dq�

�ddr_dqs�

��(1)� The� local_cs_addr� ,� local_row_addr� ,� local_bank_addr� ,� and� local_col_addr� signals� are� a� representation� of� the�

�local_addr� signal.�

�(2)� DDR� Command� shows� the� command� that� the� command� signals� are� issuing.�

�1.� The� user� logic� requests� the� first� read� by� asserting� the� local_read_req� signal,�

�and� the� size� and� address� for� this� read.� In� this� example,� the� request� is� a� burst� of�

�length� 4� (8� on� the� DDR� SDRAM� side).� The� local_ready� signal� is� asserted,� which�

�indicates� that� the� controller� has� accepted� this� request,� and� the� user� logic� can�

�request� another� read� or� write� in� the� following� clock� cycle.� If� the� local_ready�

�signal� was� not� asserted,� the� user� logic� must� keep� the� read� request,� size,� and�

�address� signals� asserted.�

�2.� The� user� logic� requests� a� second� read� to� a� different� address,� this� time� of� size� 2� (4�

�on� the� DDR� SDRAM� side).� The� local_ready� signal� remains� asserted,� which�

�indicates� that� the� controller� has� accepted� the� request.�

�3.� The� user� logic� requests� a� third� read� to� a� different� address,� this� time� of� size� 1� (2� on�

�the� DDR� SDRAM� side).� The� local_ready� signal� remains� asserted,� which�

�indicates� that� the� controller� has� accepted� the� request.�

��?� March� 2009� Altera� Corporation�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IP-SLITE2

IP SERIALLITE II

IP-SRAM/QDRII

IP QDRII SRAM CONTROLLER

IP-VITERBI/SS

IP VITERBI LOW-SPEED

IP4220CZ6,125

IC USB DUAL ESD PROTECT 6TSOP

IPA-66-1-600-10.0-A-01-T

CIRC BRKR 10A 2POLE SCREW TERM

IPR-CSC

IP COLOR SPACE CONVERTER RENEW

IPR-ED8B10B

IP 8B10B ENCODER/DECODER RENEW

IPS-VIDEO

IP VIDEO/IMAGE PROCESSING SUITE

相关代理商/技术参数

IP-SDRAM/DDR3

功能描述:开发软件 DDR3 SDRAM Control MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IP-SDRAM/HPDDR

功能描述:开发软件 DDR SDRAM Control MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IP-SDRAM/HPDDR2

功能描述:开发软件 DDR2 SDRAM Control MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IP-SDRAM/LPDDR2

功能描述:开发软件 DDR2 SDRAM Control MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IPSE.4.33SM600

制造商:Banner Engineering 功能描述:FIBER IPSE.4.33SM600 GLASS FIBER (MIN ORDER 50)

IPSE.4.62SM600

制造商:Banner Engineering 功能描述:FIBER IPSE.4.62SM600 GLASS FIBER (MIN ORDER 50)

IPS-EMBEDDED

功能描述:开发软件 Embedded IP Suite MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IPS-EVAL-EH-01

功能描述:ENERGY HARVESTING BOARD RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:THINERGY® 标准包装:1 系列:- 主要目的:数字电位器 嵌入式:- 已用 IC / 零件:AD5258 主要属性:- 次要属性:- 已供物品:板 相关产品:AD5258BRMZ1-ND - IC POT DGTL I2C1K 64P 10MSOPAD5258BRMZ10-ND - IC POT DGTL I2C 10K 64P 10MSOPAD5258BRMZ100-ND - IC POT DGTL I2C 100K 64P 10MSOPAD5258BRMZ50-ND - IC POT DGTL I2C 50K 64P 10MSOPAD5258BRMZ1-R7-ND - IC POT DGTL I2C 1K 64P 10MSOPAD5258BRMZ10-R7-ND - IC POT DGTL I2C 10K 64P 10MSOPAD5258BRMZ50-R7-ND - IC POT DGTL I2C 50K 64P 10MSOPAD5258BRMZ100-R7-ND - IC POT DGTL I2C 100K 64P 10MSOP